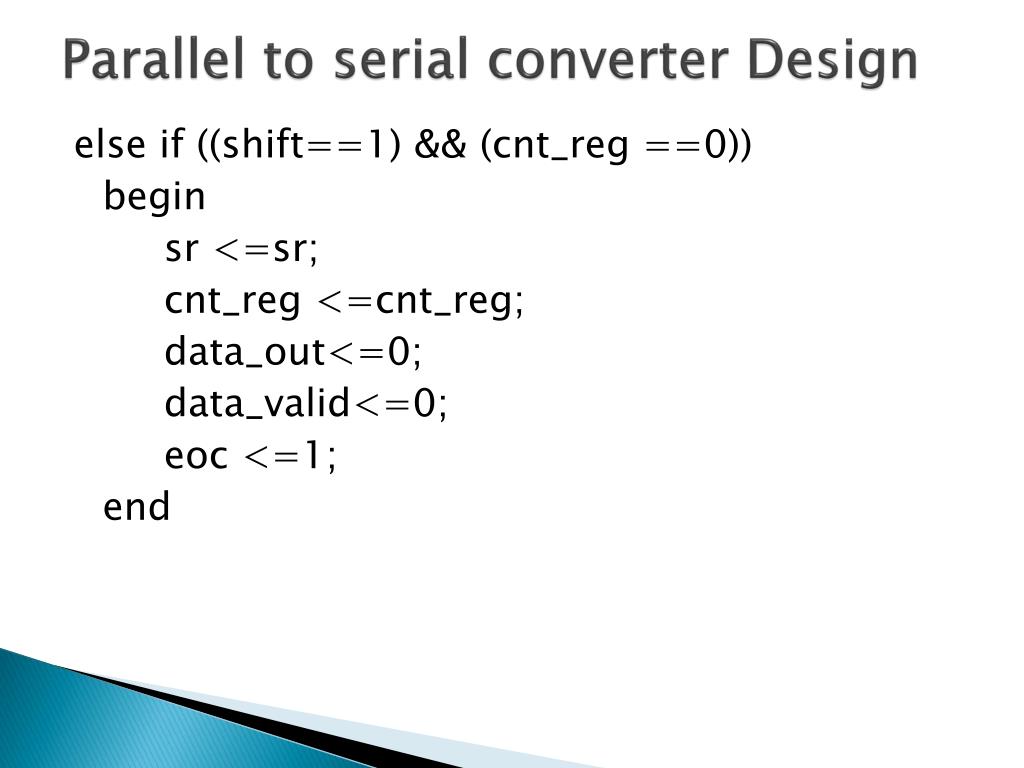

Once all the bits are loaded (all the flip-flops have one bit stored in the Q pin), then enable the bus operation.Load all the bits into the outputs of the flip-flops by moving them one bit at a time using the clock.This is summarized by stating that the conversion is carried out in three stages: For this process to happen, the converter is disabled (by means of one or more control lines) during the transfer process and enabled once all the bits are at the output bus. Once all the outputs are filled, the converter releases all the bits at once. a parallel-in, serial-out shift register, counters that count in different sequences, ALUs, various Moore and Mealy synchronous sequential machines. Parallel input Load Shift register D Serial output Reset FSM Clock 0. The converter does not release the parallel set of bits until all the bits (four in this case) are transferred, and each one is stored at the output (Q) of a corresponding flip-flop. Transcribed image text: 6.39 Write Verilog code to specify the circuit in Figure 6.97. In this figure we have not shown all the circuitry of an actual converter. Successive ticks moves the bits to the next flip-flop, until all four bits are stored at the output of each flip-flop.

tick) of the clock, the first bit (1 in this case) is transferred to the input of the second flip-flop.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed